### **APDS-9309**

Miniature Ambient Light Photo Sensor with Digital (I<sup>2</sup>C) Output

## **Data Sheet**

#### **Description**

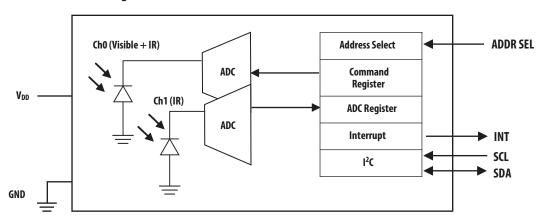

The APDS-9309 is a low-voltage Digital Ambient Light Photo Sensor that converts light intensity to digital signal output capable of direct I<sup>2</sup>C-bus interface. Each device consists of one broadband photodiode (visible plus infrared) and one infrared photodiode. Two integrating ADCs convert the photodiode currents to a digital output that represents the irradiance measured on each channel. This digital output can be input to a microprocessor where illuminance (ambient light level) in lux is derived using an empirical formula to approximate the human-eye response.

#### **Applications**

- Detection of ambient light to control display backlighting

- o Mobile devices Cell phones, PDAs, PMP

- o Computing devices Notebooks, Tablet PC, Key

- o Consumer devices LCD Monitor, Flat-panel TVs, Video Cameras, Digital Still Camera

- Automatic Residential and Commercial Lighting Management

- Automotive instrumentation clusters.

- Electronic Signs and Signals

#### **Features**

- Approximate the human-eye response

- Precise Illuminance measurement under diverse lighting conditions

- Programmable Interrupt Function with User-Defined Upper and Lower Threshold Settings

- 16-Bit Digital Output with I<sup>2</sup>C Fast-Mode at 400 kHz

- Programmable Analog Gain and Integration Time

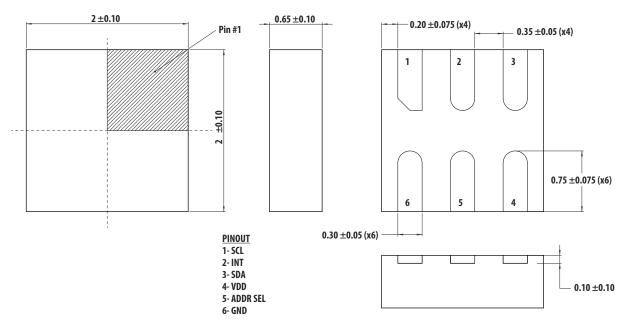

- Miniature ChipLED Package

- o Height 0.65 mm

- o Length 2.00 mm

- o Width 2.00 mm

- 50/60 Hz Lighting Ripple Rejection

- Low 2.5 V Input Voltage and 1.8 V Digital Output

- Low Active Power (0.6 mW Typical) with Power Down Mode

- RoHS Compliant

#### **Application Support Information**

The Application Engineering Group is available to assist you with the application design associated with APDS-9309 ambient light photo sensor module. You can contact them through your local sales representatives for additional details.

## **Ordering Information**

| Part Number | Packaging Type | Package                | Quantity      |

|-------------|----------------|------------------------|---------------|

| APDS-9309   | Tape and Reel  | 6-pins Chipled package | 5000 per reel |

## **Functional Block Diagram**

## **10 Pins Configuration Table**

| Pin | Symbol   | Description    |

|-----|----------|----------------|

| 1   | SCL      | Serial Clock   |

| 2   | INT      | Interrupt      |

| 3   | SDA      | Serial Data    |

| 4   | $V_{DD}$ | Voltage Supply |

| 5   | ADDR SEL | Address Select |

| 6   | GND      | Ground         |

### **Absolute Maximum Ratings**

| Parameter                    | Symbol           | Min  | Max  | Unit |  |

|------------------------------|------------------|------|------|------|--|

| Supply voltage               | $V_{DD}$         | _    | 3.8  | V    |  |

| Digital output voltage range | Vo               | -0.5 | 3.8  | V    |  |

| Digital output current       | Io               | -1   | 20   | mA   |  |

| Storage temperature range    | T <sub>stg</sub> | -40  | 85   | °C   |  |

| ESD tolerance                | human body model | _    | 2000 | V    |  |

### **Recommended Operating Conditions**

| Parameter                   | Symbol          | Min  | Тур | Max  | Unit | Condition                |

|-----------------------------|-----------------|------|-----|------|------|--------------------------|

| Supply Voltage              | $V_{DD}$        | 2.4  | 2.5 | 3.0  | V    |                          |

| Operating Temperature       | Та              | -30  | -   | 85   | °C   |                          |

| SCL, SDA input low voltage  | V <sub>IL</sub> | -0.5 | -   | 0.58 | V    |                          |

| SCL, SDA input high voltage | V <sub>IH</sub> | 1.13 | -   | 3.6  | V    | $2.4 \le V_{DD} \le 2.6$ |

|                             |                 | 1.25 | -   | 3.6  | V    | $2.4 \le V_{DD} \le 3.0$ |

### **Electrical Characteristics**

| Parameter                   | Symbol            | Min | Тур  | Max | Unit | Conditions        |

|-----------------------------|-------------------|-----|------|-----|------|-------------------|

| Supply current              | $I_{DD}$          | -   | 0.24 | 0.6 | mA   | Active            |

|                             |                   | -   | 3.2  | 15  | μΑ   | Power down        |

| INT, SDA output low voltage | V <sub>OL</sub>   | 0   | _    | 0.4 | V    | 3 mA sink current |

|                             |                   | 0   | -    | 0.6 | V    | 6 mA sink current |

| Leakage current             | I <sub>LEAK</sub> | -5  | -    | 5   | μΑ   |                   |

## Operating Characteristics, High Gain (16X), $V_{DD} = 2.5 \text{ V}$ , $Ta = 25^{\circ} \text{ C}$ , (unless otherwise noted) (see Notes 1, 2, 3, 4)

| Parameter                  | Symbol | Channel | Min | Тур  | Max   | Unit   | Conditions                                          |

|----------------------------|--------|---------|-----|------|-------|--------|-----------------------------------------------------|

| Oscillator frequency       | fosc   |         | 690 | 735  | 780   | kHz    |                                                     |

| Dark ADC count value       |        | Ch0     | 0   |      | 4     | counts | Ee = 0, Tint = 402 ms                               |

|                            |        | Ch1     | 0   |      | 4     |        |                                                     |

| Full scale ADC count value |        | Ch0     |     |      | 65535 | counts | Tint > 178 ms                                       |

|                            |        | Ch1     |     |      | 65535 |        |                                                     |

|                            |        | Ch0     |     |      | 37177 |        | Tint = 101 ms                                       |

|                            |        | Ch1     |     |      | 37177 |        |                                                     |

|                            |        | Ch0     |     |      | 5047  |        | Tint = 13.7 ms                                      |

|                            |        | Ch1     |     |      | 5047  |        |                                                     |

| ADC count value            |        | Ch0     | 750 | 1000 | 1250  | counts | λp = 640 nm, Tint = 101 ms                          |

|                            |        | Ch1     |     | 200  |       |        | Ee = $36.3  \mu \text{W/cm}^2$                      |

|                            |        | Ch0     | 700 | 1000 | 1300  |        | $\lambda p = 850 \text{ nm, Tint} = 101 \text{ ms}$ |

|                            |        | Ch1     |     | 820  |       |        | Ee = $60.2 \mu\text{W/cm}^2$                        |

#### Notes

1. Integration time Tint, is dependent on internal oscillator frequency (fosc) and on the integration field value in the timing register as described in the Register Set section. For nominal fosc = 735 kHz, nominal Tint = (number of clock cycles)/fosc.

Field value 00: Tint = (11 • 918)/fosc = 13.7 ms Field value 01: Tint = (81 • 918)/fosc = 101 ms Field value 10: Tint = (322 • 918)/fosc = 402 ms

Scaling between integration times vary proportionally as follows:

11/322 = 0.034 (field value 00), 81/322 = 0.252 (field value 01), and 322/322 = 1 (field value 10).

2. Full scale ADC count value is limited by the fact that there is a maximum of one count per two oscillator frequency periods and also by a 2-count offset.

Full scale ADC count value = ((number of clock cycles)/2 - 2)

Field value 00: Full scale ADC count value = ((11 • 918)/2 - 2) = 5047

Field value 01: Full scale ADC count value = ((81 • 918)/2 - 2) = 37177

Field value 10: Full scale ADC count value = 65535, which is limited by 16 bit register. This full scale ADC count value is reached for 131074 clock cycles, which occurs for Tint = 178 ms for nominal fosc = 735 kHz.

- 3. Low gain mode has 16x lower gain than high gain mode: (1/16 = 0.0625).

- 4. In open air (no window) above the sensor condition, the Lux value can be computed from the CH0 and Ch1 ADC values per below:

In Incandescent light source:

$$Computed \ Lux = \frac{CH0}{(GAIN \times Integration \ Time)} \times Lux\_factor\_Incan$$

$$When \frac{CH1}{CH0} > Lightsource\_Ratio$$

In Non-Incandescent light source:

$$Computed \ Lux = \frac{CH0}{(GAIN \times Integration \ Time)} \times Lux\_factor\_Non\_Incan$$

$$When \frac{CH1}{CH0} \leq Lightsource\_Ratio$$

$$where$$

$$Lighsource\_Ratio=0.55$$

where

Lighsource\_Ratio=0.55

Lux\_factor\_Incan=24.01

Lux\_factor\_Non\_Incan=170.18

Integration Time = 13.7ms, 101ms or 402ms

GAIN = 1 or 16

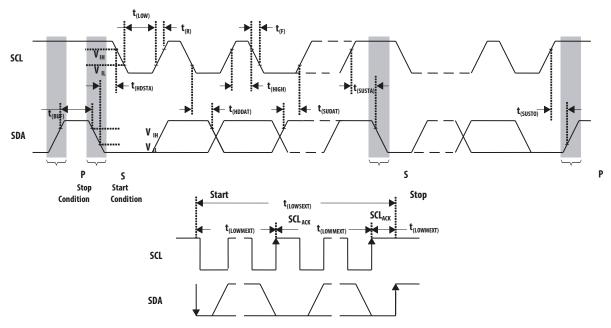

#### AC Electrical Characteristics (V<sub>DD</sub> = 3 V, Ta = 25 °C)

| Parameter †          |                                                                                              | Min. | Typ. | Max. | Unit |

|----------------------|----------------------------------------------------------------------------------------------|------|------|------|------|

| t <sub>(CONV)</sub>  | Conversion time                                                                              | 12   | 100  | 400  | ms   |

| f <sub>(SCL)</sub>   | Clock frequency                                                                              | -    | -    | 400  | kHz  |

| t <sub>(BUF)</sub>   | Bus free time between start and stop condition                                               | 1.3  | -    | -    | μs   |

| t <sub>(HDSTA)</sub> | Hold time after (repeated) start condition. After this period, the first clock is generated. | 0.6  | _    | -    | μs   |

| t(SUSTA)             | Repeated start condition setup time                                                          | 0.6  | -    | -    | μs   |

| t(SUSTO)             | Stop condition setup time                                                                    | 0.6  | -    | _    | μs   |

| t <sub>(HDDAT)</sub> | Data hold time                                                                               | 0    | -    | 0.9  | μs   |

| t(SUDAT)             | Data setup time                                                                              | 100  | -    | _    | ns   |

| t <sub>(LOW)</sub>   | SCL clock low period                                                                         | 1.3  | -    | _    | μs   |

| t <sub>(HIGH)</sub>  | SCL clock high period                                                                        | 0.6  | -    | -    | μs   |

| t <sub>F</sub>       | Clock/data fall time                                                                         | _    | -    | 300  | ns   |

| t <sub>R</sub>       | Clock/data rise time                                                                         | _    | -    | 300  | ns   |

| C <sub>j</sub>       | Input pin capacitance                                                                        | -    | -    | 10   | рF   |

|                      |                                                                                              |      |      |      |      |

<sup>&</sup>lt;sup>†</sup> Specified by design and characterization; not production tested.

### **Parameter Measurement Information**

**Figure 1. Timing Diagrams**

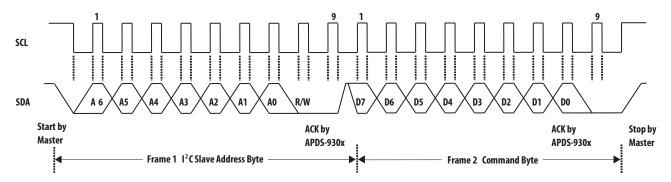

Figure 2. Example Timing Diagram for I<sup>2</sup>C Send Byte Format

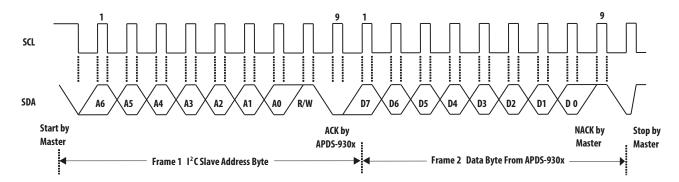

Figure 3. Example Timing Diagram for  $\ensuremath{I^2C}$  Receive Byte Format

### **Typical Characteristics**

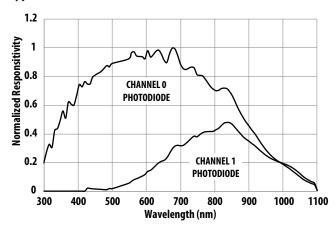

Figure 4. Normalized Responsivity vs. Spectral Responsivity

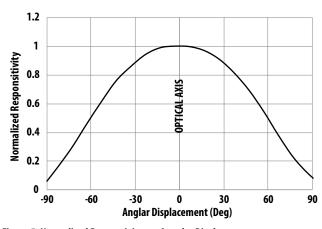

Figure 5. Normalized Responsivity vs. Angular Displacement

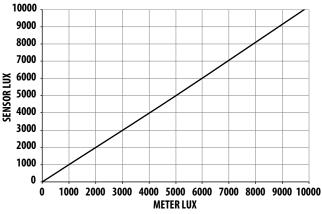

Figure 6. Sensor LUX vs. Meter LUX in white light

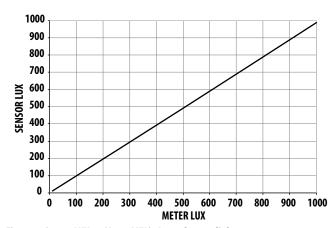

Figure 7. Sensor LUX vs. Meter LUX in Incandescent light

#### **Principles of Operation**

#### **Analog-to-Digital Converter**

The APDS-9309 contains two integrating analog-to-digital converters (ADC) that integrate the currents from the channel 0 and channel 1 photodiodes. Integration of both channels occurs simultaneously, and upon completion of the conversion cycle the conversion result is transferred to the channel 0 and channel 1 data registers, respectively. The transfers are double buffered to ensure that invalid data is not read during the transfer. After the transfer, the device automatically begins the next integration cycle.

#### **Digital Interface**

Interface and control of the APDS-9309 is accomplished through a two-wire serial interface to a set of registers that provide access to device control functions and output data. The serial interface is compatible to I<sup>2</sup>C bus Fast-Mode. The APDS-9309 offers three slave addresses that are selectable via an external pin (ADDR SEL). The slave address options are shown in Table 1.

**Table 1. Slave Address Selection**

| ADDR SEL Terminal Level | Slave Address |  |

|-------------------------|---------------|--|

| GND                     | 0101001       |  |

| Float                   | 0111001       |  |

| $V_{DD}$                | 1001001       |  |

Note:

The Slave Addresses are 7 bits and please note the  $I^2C$  protocols. A read/write bit should be appended to the slave address by the master device to properly communicate with the APDS-9309 device.

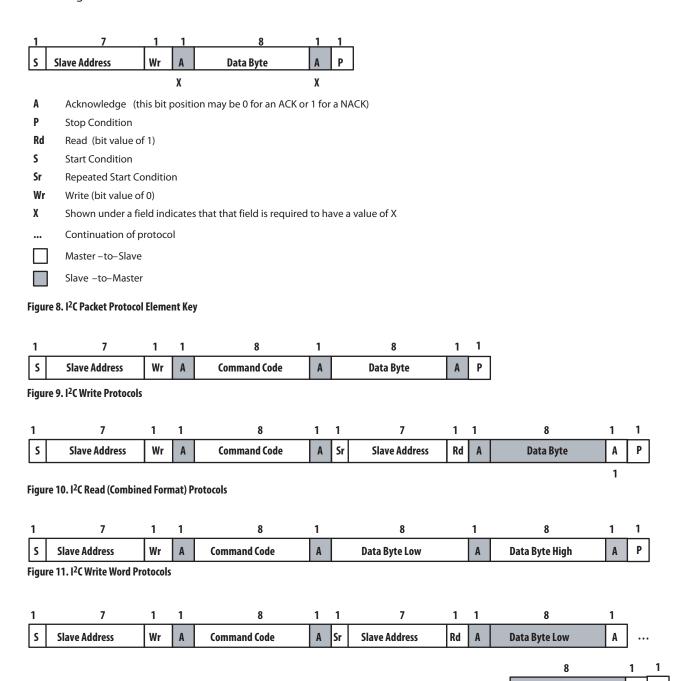

#### I<sup>2</sup>C Protocols

Each Send and Write protocol is, essentially, a series of bytes. A byte sent to the APDS-9309 with the most significant bit (MSB) equal to 1 will be interpreted as a COMMAND byte. The lower four bits of the COMMAND byte form the register select address (see Table 2), which is used to select the destination for the subsequent byte(s) received. The APDS-9309 responds to any Receive Byte requests with the contents of the register specified by the stored register select address.

The APDS-9309 implements the following protocols of the Philips Semiconductor I<sup>2</sup>C specification:

- I<sup>2</sup>C Write Protocol

- I<sup>2</sup>C Read Protocol

For a complete description of I<sup>2</sup>C protocols, please review the I<sup>2</sup>C Specification athttp://www.semiconductors.philips.com

**Data Byte High**

Figure 12. I<sup>2</sup>C Read Word Protocols

### **Register Set**

The APDS-9309 is controlled and monitored by sixteen registers (three are reserved) and a command register accessed through the serial interface. These registers provide for a variety of control functions and can be read to determine results of the ADC conversions. The register set is summarized in Table 2.

**Table 2. Register Address**

| Register Name  | Register Function                                                                                                                 |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------|

| COMMAND        | Specifies register address                                                                                                        |

| CONTROL        | Control of basic functions                                                                                                        |

| TIMING         | Integration time/gain control                                                                                                     |

| THRESHLOWLOW   | Low byte of low interrupt threshold                                                                                               |

| THRESHLOWHIGH  | High byte of low interrupt threshold                                                                                              |

| THRESHHIGHLOW  | Low byte of high interrupt threshold                                                                                              |

| THRESHHIGHHIGH | High byte of high interrupt threshold                                                                                             |

| INTERRUPT      | Interrupt control                                                                                                                 |

| -              | Reserved                                                                                                                          |

| CRC            | Factory test – not a user register                                                                                                |

| -              | Reserved                                                                                                                          |

| ID             | Part number/ Rev ID                                                                                                               |

| -              | Reserved                                                                                                                          |

| DATA0LOW       | Low byte of ADC channel 0                                                                                                         |

| DATA0HIGH      | High byte of ADC channel 0                                                                                                        |

| DATA1LOW       | Low byte of ADC channel 1                                                                                                         |

| DATA1HIGH      | High byte of ADC channel 1                                                                                                        |

|                | COMMAND CONTROL TIMING THRESHLOWLOW THRESHLOWHIGH THRESHHIGHLOW THRESHHIGHHIGH INTERRUPT - CRC - ID - DATAOLOW DATAOHIGH DATA1LOW |

The mechanics of accessing a specific register depends on the specific  $I^2C$  protocol used. Refer to the section on  $I^2C$  protocols. In general, the COMMAND register is written first to specify the specific control/status register for following read/write operations.

### **Command Register**

The command register specifies the address of the target register for subsequent read and write operations. The Send Byte protocol is used to configure the COMMAND register. The command register contains eight bits as described in Table 3. The command register defaults to 00h at power on.

### **Table 3. Command Register**

|              | 7   | 6     | 5    | 4        | 3 | 2   | 1    | 0 |         |

|--------------|-----|-------|------|----------|---|-----|------|---|---------|

|              | CMD | CLEAR | WORD | Reserved |   | ADD | RESS |   | COMMAND |

| Reset Value: | 0   | 0     | 0    | 0        | 0 | 0   | 0    | 0 |         |

| Field    | BIT | Description                                                                                                                                                           |

|----------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CMD      | 7   | Select command register. Must write as 1.                                                                                                                             |

| CLEAR    | 6   | Interrupt clear. Clears any pending interrupt. This bit is a write–one–to–clear bit. It is self clearing.                                                             |

| WORD     | 5   | I <sup>2</sup> C Write/Read Word Protocol.  1 indicates that this I <sup>2</sup> C transaction is using either the I <sup>2</sup> C Write Word or Read Word protocol. |

| Reserved | 4   | Reserved. Write as 0.                                                                                                                                                 |

| ADDRESS  | 3:0 | Register Address. This field selects the specific control or status register for following write and read commands according to Table 2.                              |

### **Control Register (0h)**

The CONTROL register contains two bits and is primarily used to power the APDS-9309 device up and down as shown in Table 4.

#### **Table 4. Control Register**

|              | 7        | 6        | 5        | 4        | 3        | 2        | 1   | 0   |         |

|--------------|----------|----------|----------|----------|----------|----------|-----|-----|---------|

| Oh           | Reserved | Reserved | Reserved | Reserved | Reserved | Reserved | PO' | WER | CONTROL |

| Reset Value: | 0        | 0        | 0        | 0        | 0        | 0        | 0   | 0   | _       |

| Field    | BIT | Description                                                                                                                                      |

|----------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------|

| Reserved | 7:2 | Reserved. Write as 0.                                                                                                                            |

| POWER    | 1:0 | Power up/power down. By writing a 03h to this register, the device is powered up. By writing a 00h to this register, the device is powered down. |

Note: If a value of 03h is written, the value returned during a read cycle will be 03h. This feature can be used to verify that the device is communicating properly.

#### Timing Register (1h)

The TIMING register controls both the integration time and the gain of the ADC channels. A common set of control bits is provided that controls both ADC channels. The TIMING register defaults to 02h at power on.

**Table 5. Timing Register**

| Field    | BIT | Description                                                                                                                       |

|----------|-----|-----------------------------------------------------------------------------------------------------------------------------------|

| Reserved | 7-5 | Reserved. Write as 0.                                                                                                             |

| GAIN     | 4   | Switches gain between low gain and high gain modes.<br>Writing a 0 selects low gain (1x);<br>Writing a 1 selects high gain (16x). |

| MANUAL   | 3   | Manual timing control.<br>Writing a 1 begins an integration cycle.<br>Writing a 0 stops an integration cycle.                     |

|          |     | NOTE: This field only has meaning when INTEG = 11. It is ignored at all other times.                                              |

| Resv     | 2   | Reserved. Write as 0.                                                                                                             |

| INTEG    | 1:0 | Integrate time. This field selects the integration time for each conversion.                                                      |

Integration time is dependent on the INTEG FIELD VALUE and the internal clock frequency. Nominal integration times and respective scaling between integration times scale proportionally as shown in Table 6. See Note 5 and Note 6 on page 4 for detailed information regarding how the scale values were obtained.

**Table 6. Integration Time**

| Integ Field Value | Scale | Nominal Integration Time |

|-------------------|-------|--------------------------|

| 00                | 0.034 | 13.7 ms                  |

| 01                | 0.252 | 101 ms                   |

| 10                | 1     | 402 ms                   |

| 11                | _     | N/A                      |

The manual timing control feature is used to manually start and stop the integration time period. If a particular integration time period is required that is not listed in Table 6, then this feature can be used. For example, the manual timing control can be used to synchronize the APDS-9309 device with an external light source (e.g. LED). A start command to begin integration can be initiated by writing a 1 to this bit field. Correspondingly, the integration can be stopped by simply writing a 0 to the same bit field.

#### Interrupt Threshold Register (2 h – 5 h)

The interrupt threshold registers store the values to be used as the high and low trigger points for the comparison function for interrupt generation. If the value generated by channel 0 crosses below or is equal to the low threshold specified, an interrupt is asserted on the interrupt pin. If the value generated by channel 0 crosses above the high threshold specified, an interrupt is asserted on the interrupt pin. Registers THRESHLOWLOW and THRESHLOWHIGH provide the low byte and high byte, respectively, of the lower interrupt threshold. Registers THRESHHIGHLOW and THRESHHIGHHIGH provide the low and high bytes, respectively, of the upper interrupt threshold. The high and low bytes from each set of registers are combined to form a 16-bit threshold value. The interrupt threshold registers default to 00h on power up.

Table 7. Interrupt Threshold Register

| Register       | Address | Bits | Description                                    |

|----------------|---------|------|------------------------------------------------|

| THRESHLOWLOW   | 2h      | 7:0  | ADC channel 0 lower byte of the low threshold  |

| THRESHLOWHIGH  | 3h      | 7:0  | ADC channel 0 upper byte of the low threshold  |

| THRESHHIGHLOW  | 4h      | 7:0  | ADC channel 0 lower byte of the high threshold |

| THRESHHIGHHIGH | 5h      | 7:0  | ADC channel 0 upper byte of the high threshold |

Note: Since two 8-bit values are combined for a single 16-bit value for each of the high and low interrupt thresholds, the Send Byte protocol should not be used to write to these registers. Any values transferred by the Send Byte protocol with the MSB set would be interpreted as the COMMAND field and stored as an address for subsequent read/write operations and not as the interrupt threshold information as desired. The Write Word protocol should be used to write byte-paired registers. For example, the THRESHLOWLOW and THRESHLOWHIGH registers (as well as the THRESHHIGHLOW and THRESHHIGHLIGH registers) can be written together to set the 16-bit ADC value in a single transaction.

#### **Interrupt Control Register (6h)**

The INTERRUPT register controls the extensive interrupt capabilities of the APDS-9309. The APDS-9309 permits traditional level-style interrupts. The interrupt persist bit field (PERSIST) provides control over when interrupts occur. A value of 0 causes an interrupt to occur after every integration cycle regardless of the threshold settings. A value of 1 results in an interrupt after one integration time period outside the threshold window. A value of N (where N is 2 through 15) results in an interrupt only if the value remains outside the threshold window for N consecutive integration cycles. For example, if N is equal to 10 and the integration time is 402 ms, then the total time is approximately 4 seconds.

When a level Interrupt is selected, an interrupt is generated whenever the last conversion results in a value outside of the programmed threshold window. The interrupt is active-low and remains asserted until cleared by writing the COMMAND register with the CLEAR bit set.

Note: Interrupts are based on the value of Channel 0 only.

**Table 8. Interrupt Control Register**

|              | 7        | 6        | 5  | 4  | 3 | 2   | 1    | 0 |           |

|--------------|----------|----------|----|----|---|-----|------|---|-----------|

| 1 h          | Reserved | Reserved | IN | TR |   | PER | SIST |   | INTERRUPT |

| Reset Value: | 0        | 0        | 0  | 0  | 0 | 0   | 0    | 0 |           |

| Field    | BIT | Description                                                                                           |

|----------|-----|-------------------------------------------------------------------------------------------------------|

| Reserved | 7:6 | Reserved. Write as 0.                                                                                 |

| INTR     | 5:4 | INTR Control Select. This field determines mode of interrupt logic according to Table 9, below.       |

| PERSIST  | 3:0 | Interrupt persistence. Controls rate of interrupts to the host processor as shown in Table 10, below. |

### **Table 9. Interrupt Control Select**

| Intr Field Value | Read Value                |

|------------------|---------------------------|

| 00               | Interrupt output disabled |

| 01               | Level Interrupt           |

### **Table 10. Interrupt Persistence Select**

| Persist Field Value | Interrupt Persist Function               |

|---------------------|------------------------------------------|

| 0000                | Every ADC cycle generates interrupt      |

| 0001                | Any value outside of threshold range     |

| 0010                | 2 integration time periods out of range  |

| 0011                | 3 integration time periods out of range  |

| 0100                | 4 integration time periods out of range  |

| 0101                | 5 integration time periods out of range  |

| 0110                | 6 integration time periods out of range  |

| 0111                | 7 integration time periods out of range  |

| 1000                | 8 integration time periods out of range  |

| 1001                | 9 integration time periods out of range  |

| 1010                | 10 integration time periods out of range |

| 1011                | 11 integration time periods out of range |

| 1100                | 12 integration time periods out of range |

| 1101                | 13 integration time periods out of range |

| 1110                | 14 integration time periods out of range |

| 1111                | 15 integration time periods out of range |

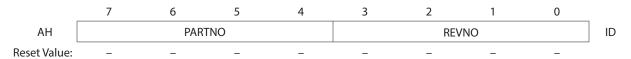

## ID Register (Ah)

The ID register provides the value for both the part number and silicon revision number for that part number. It is a read-only register, whose value never changes.

Table 11. ID Register

| Field  | BIT | Description                    |

|--------|-----|--------------------------------|

| PARTNO | 7:4 | Part Number Identification     |

| REVNO  | 3:0 | Revision number identification |

#### ADC Channel Data Registers (Ch – Fh)

The ADC channel data are expressed as 16-bit values spread across two registers. The ADC channel 0 data registers, DATA0LOW and DATA0HIGH provide the lower and upper bytes, respectively, of the ADC value of channel 0. Registers DATA1LOW and DATA1HIGH provide the lower and upper bytes, respectively, of the ADC value of channel 1. All channel data registers are read—only and default to 00h on power up.

**Table 12. ADC Channel Data Registers**

| Register  | Address | Bits | Description              |  |

|-----------|---------|------|--------------------------|--|

| DATA0LOW  | Ch      | 7:0  | ADC channel 0 lower byte |  |

| DATA0HIGH | Dh      | 7:0  | ADC channel 0 upper byte |  |

| DATA1LOW  | Eh      | 7:0  | ADC channel 1 lower byte |  |

| DATA1HIGH | Fh      | 7:0  | ADC channel 1 upper byte |  |

The upper byte data registers can only be read following a read to the corresponding lower byte register. When the lower byte register is read, the upper eight bits are strobed into a shadow register, which is read by a subsequent read to the upper byte. The upper register will read the correct value even if additional ADC integration cycles end between the reading of the lower and upper registers.

Note: The Read Word protocol can be used to read byte–paired registers. For example, the DATAOLOW and DATAOHIGH registers (as well as the DATA1LOW and DATA1HIGH registers) may be read together to obtain the 16-bit ADC value in a single transaction

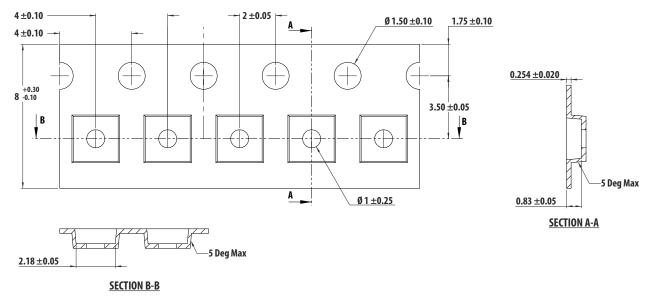

## Package Outline - APDS-9309

#### Note:

1. All dimensions are in millimeters.

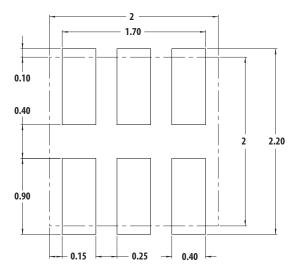

### **PCB Pad Layout**

#### Note:

1. All linear dimensions are in millimeters.

### **Tape Dimensions**

All dimensions unit: mm

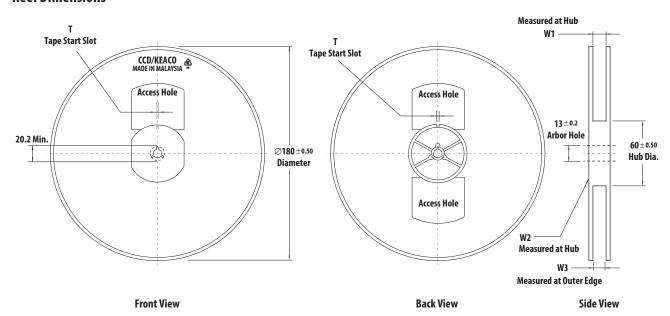

### **Reel Dimensions**

| TAPE WIDTH | T        | W1        | W2       | W3       |

|------------|----------|-----------|----------|----------|

| 8 MM       | 3 ± 0.50 | 8.4 + 1.5 | 14.4 MAX | 7.9 MIN  |

|            |          | - 0.0     |          | 10.9 MAX |

#### **Moisture Proof Packaging Chart**

All APDS-9309 options are shipped in moisture proof package. Once opened, moisture absorption begins.

This part is compliant to JEDEC Level 3.

#### **Recommended Storage Conditions**

| Storage Temperature | 10° C to 30° C |  |

|---------------------|----------------|--|

| Relative Humidity   | Below 60% RH   |  |

### **Time from Unsealing to Soldering**

After removal from the bag, the parts should be soldered within seven days if stored at the recommended storage conditions. When MBB (Moisture Barrier Bag) is opened and the parts are exposed to the recommended storage conditions more than seven days the parts must be baked before reflow to prevent damage to the parts.

#### **Baking conditions**

If the parts are not stored per the recommended storage conditions they must be baked before reflow to prevent damage to the parts.

| Package  | Temp. | Time     |

|----------|-------|----------|

| In Reels | 60°C  | 48 hours |

| In Bulk  | 100°C | 4 hours  |

Note: Baking should only be done once.

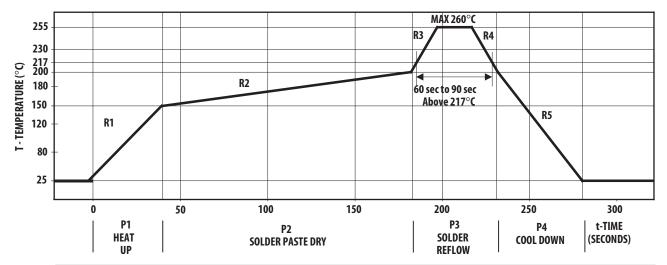

#### **Recommended Reflow Profile**

| Process Zone                                 | Symbol | ΔΤ               | Maximum ∆T/∆time<br>or Duration |

|----------------------------------------------|--------|------------------|---------------------------------|

| Heat Up                                      | P1, R1 | 25° C to 150° C  | 3°C/s                           |

| Solder Paste Dry                             | P2, R2 | 150° C to 200° C | 100 s to 180 s                  |

| Solder Reflow                                | P3, R3 | 200° C to 260° C | 3°C/s                           |

|                                              | P3, R4 | 260° C to 200° C | -6°C/s                          |

| Cool Down                                    | P4, R5 | 200° C to 25° C  | -6°C/s                          |

| Time maintained above liquidus point, 217° C |        | > 217° C         | 60 s to 90 s                    |

| Peak Temperature                             |        | 260° C           | _                               |

| Time within 5° C of actual Peak Temperature  |        | -                | 20 s to 40 s                    |

| Time 25° C to Peak Temperature               |        | 25° C to 260° C  | 8 mins                          |

The reflow profile is a straight-line representation of a nominal temperature profile for a convective reflow solder process. The temperature profile is divided into four process zones, each with different  $\Delta T/\Delta$ time temperature change rates or duration. The  $\Delta T/\Delta$ time rates or duration are detailed in the above table. The temperatures are measured at the component to printed circuit board connections.

In process zone P1, the PC board and component pins are heated to a temperature of 150° C to activate the flux in the solder paste. The temperature ramp up rate, R1, is limited to 3° C per second to allow for even heating of both the PC board and component pins.

Process zone P2 should be of sufficient time duration (100 to 180 seconds) to dry the solder paste. The temperature is raised to a level just below the liquidus point of the solder.

Process zone P3 is the solder reflow zone. In zone P3, the temperature is quickly raised above the liquidus point of solder to 260° C (500° F) for optimum results. The dwell

time above the liquidus point of solder should be between 60 and 90 seconds. This is to assure proper coalescing of the solder paste into liquid solder and the formation of good solder connections. Beyond the recommended dwell time the intermetallic growth within the solder connections becomes excessive, resulting in the formation of weak and unreliable connections. The temperature is then rapidly reduced to a point below the solidus temperature of the solder to allow the solder within the connections to freeze solid.

Process zone P4 is the cool down after solder freeze. The cool down rate, R5, from the liquidus point of the solder to 25° C (77° F) should not exceed 6° C per second maximum. This limitation is necessary to allow the PC board and component pins to change dimensions evenly, putting minimal stresses on the component.

It is recommended to perform reflow soldering no more than twice.

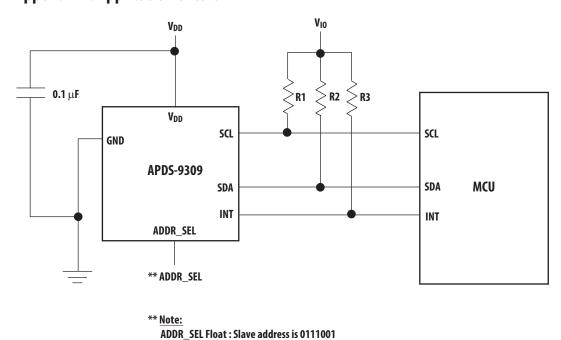

### Appendix A: Application circuit

Figure A1. Application circuit for APDS-9309

The power supply lines must be decoupled with a 0.1  $\mu$ F capacitor placed as close to the device package as possible, as shown in Figure B1. The bypass capacitor should have low effective series resistance (ESR) and low effective series inductance (ESI), such as the common ceramic types, which provide a low impedance path to ground at high frequencies to handle transient currents caused by internal logic switching.

Pull-up resistors, R1 and R2, maintain the SDA and SCL lines at a high level when the bus is free and ensure the signals are pulled up from a low to a high level within the required rise time. For a complete description of I<sup>2</sup>C maximum and minimum R1 and R2 values, please review the I<sup>2</sup>C Specification at http://www.semiconductors.philips.com.

A pull-up resistor, R3, is also required for the interrupt (INT), which functions as a wired-AND signal in a similar fashion to the SCL and SDA lines. A typical impedance value between 10 k $\Omega$  and 100 k $\Omega$  can be used.

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Avago Technologies:

APDS-9309